一般来说,官方宣扬数据都是最理想的状况,有时候还会掺杂一些水分,可是你见过实测比官方数字更美丽的吗?

台积电已在本月开端5nm工艺的试产,第二季度内投入规划量产,苹果A14、华为麒麟1020、AMD Zen 4等处理器都会使用它,并且音讯称初期产能现已被客户彻底包圆,尤其是苹果占了最大头。

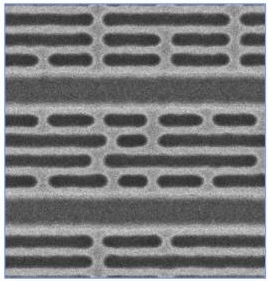

台积电没有发布5nm工艺的详细目标,只知道会大规划集成EUV极紫外光刻技能,不过在一篇论文中披露了一张晶体管结构侧视图。

WikiChips通过剖析后估量,台积电5nm的栅极距离为48nm,金属距离则是30nm,鳍片距离25-26nm,单元高度约为180nm,照此核算,台积电5nm的晶体管密度将是每平方毫米1.713亿个。

比较于初代7nm的每平方毫米9120万个,这一数字增加了足足88%,而台积电官方宣扬的数字是84%。

尽管这些年摩尔定律逐渐失效,尽管台积电的工艺常常面对质疑,但不得不敬服台积电的推动速度,要知道16nm工艺量产也仅仅不到5年前的工作,那时候的晶体管密度才不过每平方毫米2888万个,5nm现已是它的简直六倍!

别的,台积电10nm工艺的晶体管密度为每平方毫米5251万个,5nm是它的近3.3倍。

“乌镇时间”再次开启,腾讯以科技文化双引擎,激发千行百业新动能

“乌镇时间”再次开启,腾讯以科技文化双引擎,激发千行百业新动能 乘风破浪的“厂二代”|《你好!厂长》第八期全国首映,见证逆风翻盘的

乘风破浪的“厂二代”|《你好!厂长》第八期全国首映,见证逆风翻盘的 索泰×索尼影业《毒液:最后一舞》超能守护,强者共舞!

索泰×索尼影业《毒液:最后一舞》超能守护,强者共舞! 微软应用商店引入腾讯应用宝专区,拓展 Windows 应用生态

微软应用商店引入腾讯应用宝专区,拓展 Windows 应用生态 进博会看技术变化,从5G手机到AI终端,高通技术支持行业拓展

进博会看技术变化,从5G手机到AI终端,高通技术支持行业拓展 3G追赶,4G并行,5G赶超!高通孟樸进博会谈与中国伙伴合作历程

3G追赶,4G并行,5G赶超!高通孟樸进博会谈与中国伙伴合作历程 PhotonPay光子易与Coshine开先软件达成合作,共同优化全球支付体验

PhotonPay光子易与Coshine开先软件达成合作,共同优化全球支付体验